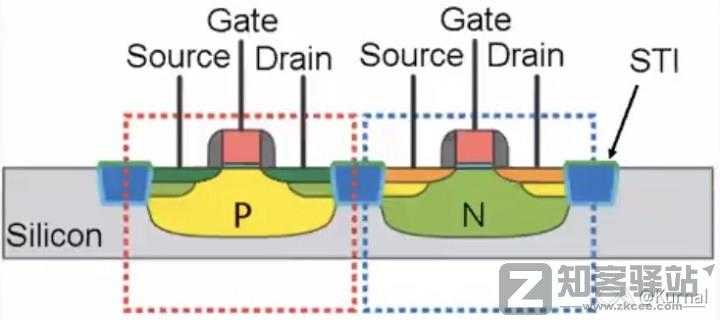

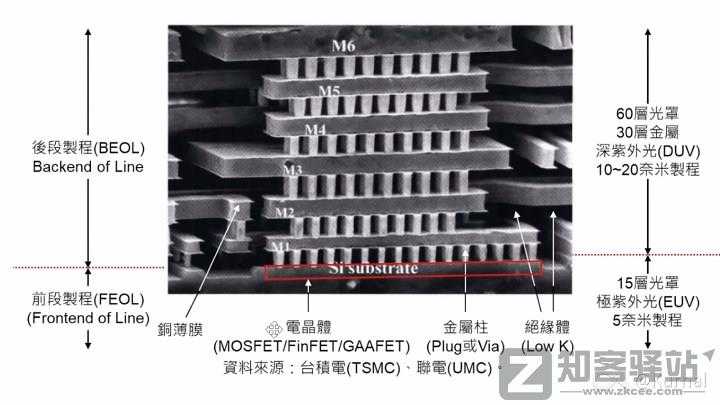

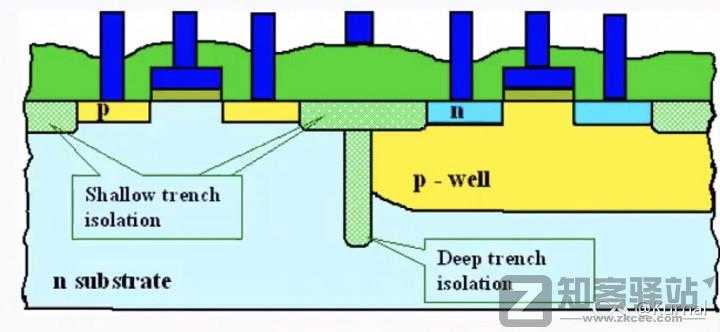

集成电路是依靠平面工艺一层一层的堆叠起来的,对于逻辑器件来说,首先是在Si衬底上active area,然后离子注入实现N型与P型区域,再做出gate,随后又是离子注,完成一个晶体管的源极与漏级,这称为前道工艺,

最简单的pn节

后道则是若干层的导电metal,一般用Cu作为其导电金属,而中道基本都是用金属W把S,G,D与m1层互联。在集成电路的制造完整流程中,需要多次光刻,有些光刻图形尺寸较大,例如栅极之前的离子注入层,在一些关键地方则用较小的光刻层图形,例如栅极层和M1层之类,其通常影响到其性能与yield,被称为关键光刻层,具体流程比如确定晶体管区域的光刻层(STI)栅极光刻层之类,

做出来的就是这样

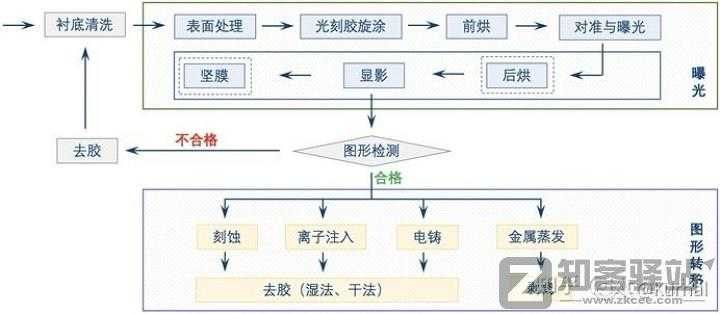

下面是代工的光刻了基本的光刻流程:薄膜沉积,光刻胶覆盖,曝光,烘烤显影,刻蚀(或者离子注入),封装

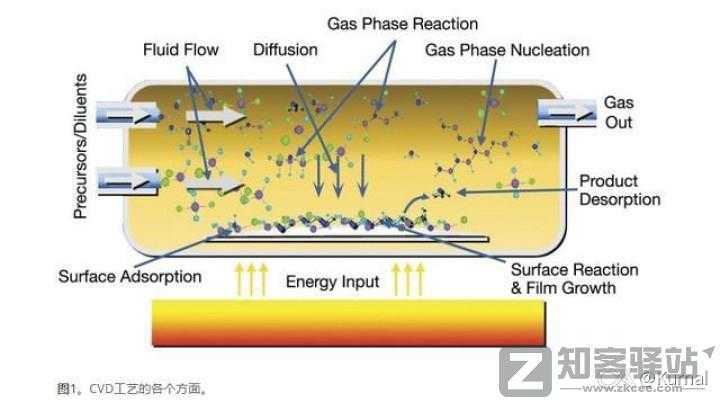

薄膜其工艺复杂,作用是在wafer表面通过化学/物理的方式相互堆叠SiO2,SiN等绝缘介质薄膜和Al,Cu等金属导电膜,在这些薄膜表面进行mask的图形转移,就是光刻。在不同的工艺环节需要PVD,CVD,ALD之类来互相补充

薄膜沉积

主要的薄膜分为半导体,介质,金属(氧化物)三大类半导体薄膜主要是用于制备源极/漏极沟道区,单晶外延层和MOS栅极等。分为单晶硅,多晶硅,非晶硅等,多晶硅基本用于MOS的栅极,非晶硅/Si/SiGe蛀牙用于光伏和填充前端工艺的源极/漏极沟道区

这玩意就是

介质薄膜运用于前段的浅槽隔离,栅氧化层,侧墙,阻挡层,金属层,前介质层,硬掩膜(这玩意运用很多现在就只记得这些)介质薄膜是一种绝缘性质的薄膜,屏蔽芯片的器件与metal之间的杂质相互扩散在介质薄膜中运用最多的就是SiO2,用于STI,栅氧化层,侧墙,阻挡层,硬掩膜等沉积过程中要防止应力出现裂纹,同时满足一部分的台阶覆盖率需求,可以在SiO2中通入硅烷起与氧气制备,或者通入TEOS(Si(OC2H5)4 四乙氧基硅烷,常见的比如在SiO2中掺入磷杂质形成PSGPVD就是物理方式,通过真空蒸镀和溅射等物理方式沉积金属化合物薄膜,目前主流的是磁控溅射和离子化PVD磁控溅射的原理是电子在电场的约束下,其表面元子逸出靶材,在基层片表面形成膜层光刻的具体步骤:

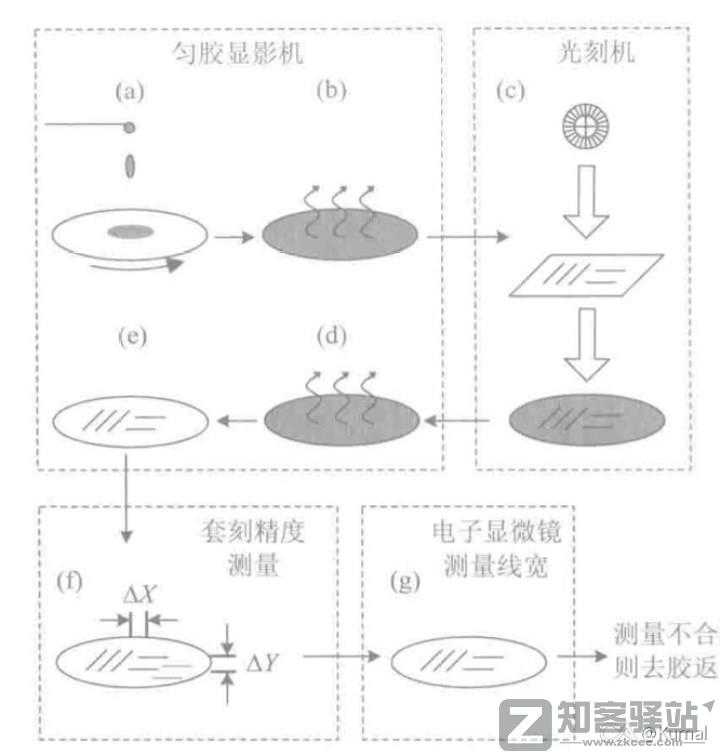

大概的流程

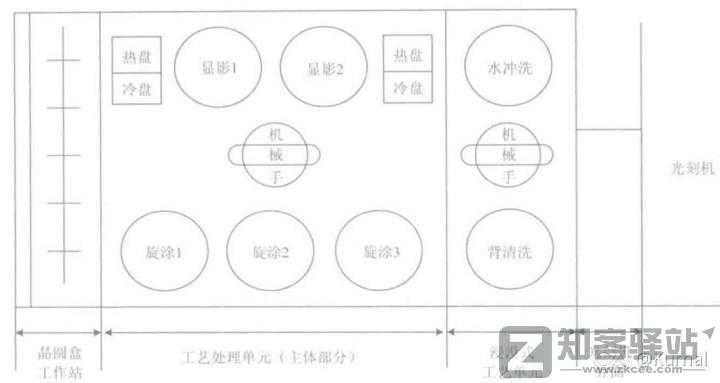

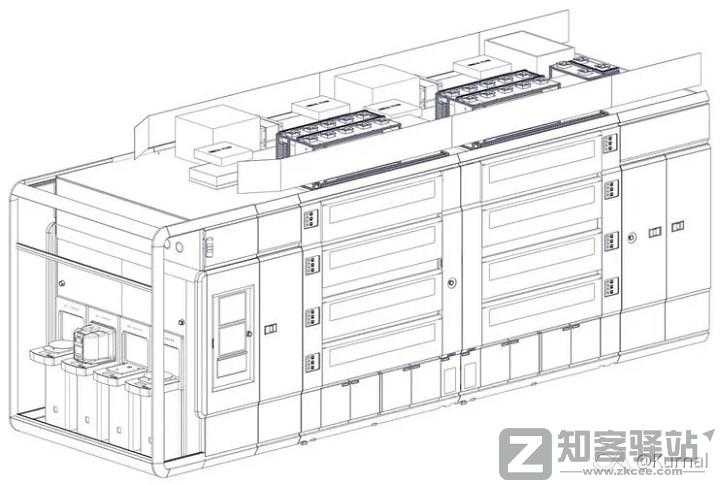

首先写一下匀胶显影机(也就是薄膜覆盖)匀胶显影机一般由4个部分构成,第一部分是晶圆盒工作站,机械手从放在这里的晶圆盒中把wafer取出来,传送到主体,工艺处理部分,例如增粘模块,热盘冷盘,旋涂,显影之类都在这里,第三部分就是光刻工艺配套的单元,包括晶圆表面水冲洗单元,背冲洗单元,第四个部分就是和光刻机的对接接口,比如buffer,暂时存储晶圆的缓存层啊,WEE,晶圆边缘曝光啊之类

大概的模拟图

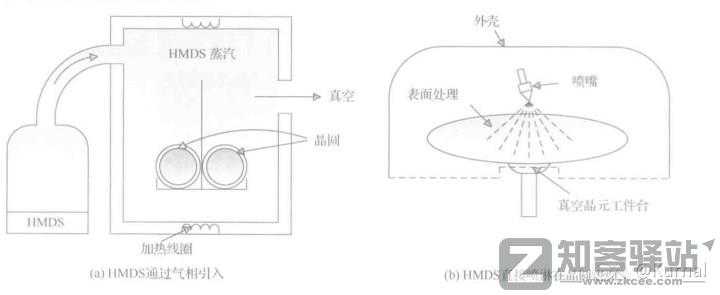

一整套流程还是以193i浸没式光刻流程为例,先经过抗反射层旋涂,烘烤,光刻胶旋涂,烘烤,抗水图层旋涂,烘烤,曝光,烘烤,显影烘烤温度必须控制好,不能高于Tg(光刻胶玻璃转化温度(不然会软化,导致其形状的破坏)一套流程基本都是用tfr来控制的,第一个步骤:增粘有些晶圆表面是亲水的,就不利于光刻胶的旋涂,得进行一个增粘,就得用到增粘模块,增粘模块是一种真空腔,把晶圆放进去后腔体封闭,等wafer加热到一定温度后,引入HMDS气体,粘附在wafer表面,让其亲油,有时候还有用HMDS直接喷淋,我没资料,不敢说

两种增粘方式

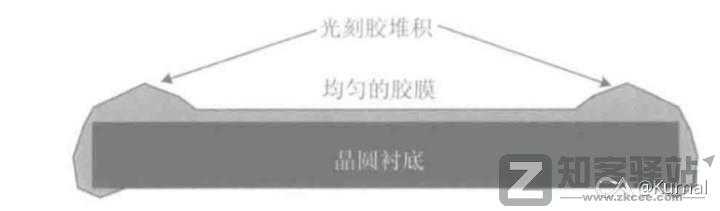

第二个步骤:光刻胶的旋涂

长这样的

旋涂单元是匀胶显影设备中一个复杂的单元,负责对wafer表面进行一个光刻胶的涂覆,实现指定的厚度与均匀性,如果其厚度不达标就会出现倒塌之类的,就算10a的厚度也算(很好理解把,凸透镜)

边缘清洗(去边)把边上多的光刻胶给清洗掉,背面的清洗就是把背面的脏东西(在制作流程中染上的,比如光刻胶)清洗掉

不洗就会这样

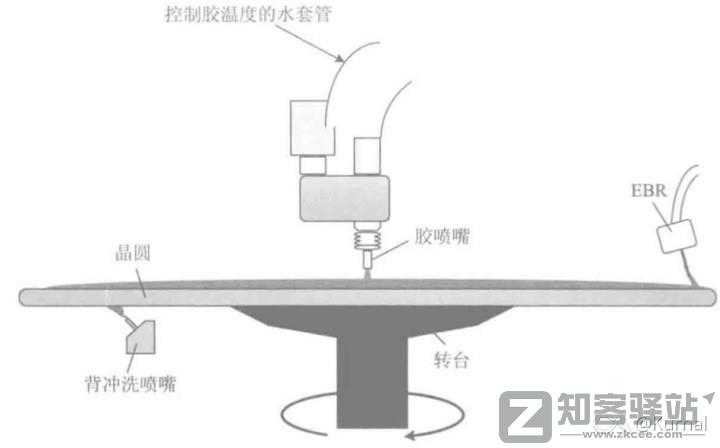

涂胶单元包括一个可以选抓的样品台和一堆喷嘴,转台用来放wafer,几个喷嘴用来喷各种有机溶剂和光刻胶,有机溶液可以使其wafer表面湿润,易于随后的光刻胶涂布,基本指标:转速可调为10-4000rpm,精度土1rpm。Wafer在涂胶单元中的流程(wafer放到转台上-预湿wafer表面-喷淋光刻胶-告诉旋转-喷溶剂去边-背喷冲洗晶圆-机械手移走)

长这样

如果喷胶的时候晶圆不动,叫静态喷胶,若晶圆旋转,则叫动态喷胶,对于300mm的wafer来说,每一次喷胶一般介于0.5-4ml,喷胶后,晶圆进行一个低速旋转,使其光刻胶覆盖整个晶圆,然后高速旋转,得到想要的厚度与均匀度,一个典型的旋涂工艺中,需要喷涂过量的胶,以保证其能在离心力的作用下有足够的胶流到晶圆边上,一般只有20-50的胶留在晶圆表面,其余的都被甩离晶圆,留到废液槽里(节俭方式:先涂2.5ml的有机溶液,然后就只需要1ml的光刻胶了)(或者用spc来实时监控)(还有一种方式就是UCP,没了解)

然后就是去边和晶圆背面冲洗了,第一次去边是在晶圆生产厂出货的时候防止应力导致碎裂,遂在wafer边上圆角了这次是光刻胶的去边,其实很好理解,在旋涂的时候,多余的胶会被离心力推到晶圆的边缘,有一部分被甩离wafe,还有一部分留在边上,有时候有些胶甚至会在表面张力的作用下流到背面进行污染,边缘的胶会在烘烤的时候脱落,污染热盘等其他后续设备,而且堆积在背面的胶会导致晶圆在曝光机台上无法水平放置,无法对焦,在曝光的时候产生坏点,所以得进行一个EBR,就是光刻胶去边

就是这样

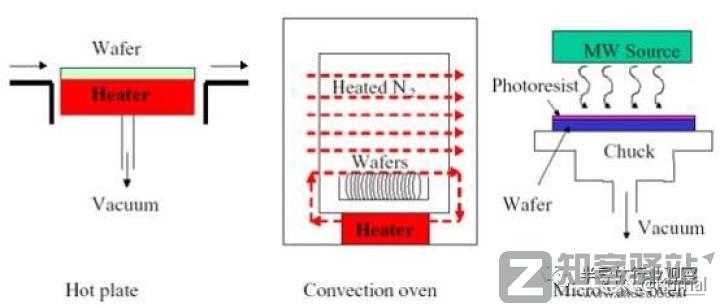

然后就是烘烤与冷却,字面意思,具体分两种,第一种是曝光后烘烤(PEB),曝光的时候,光子在光刻胶内激发了化学反应,产生了酸H+.有些地方的光刻机和匀胶显影机是不联机的,曝光后wafer得不到立刻烘烤,存在后烘延迟现象(PEB delay)通常会导致显影后光刻胶成为T型。

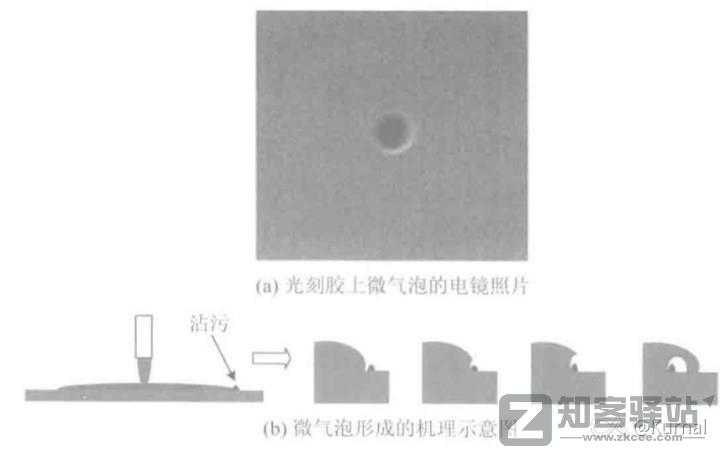

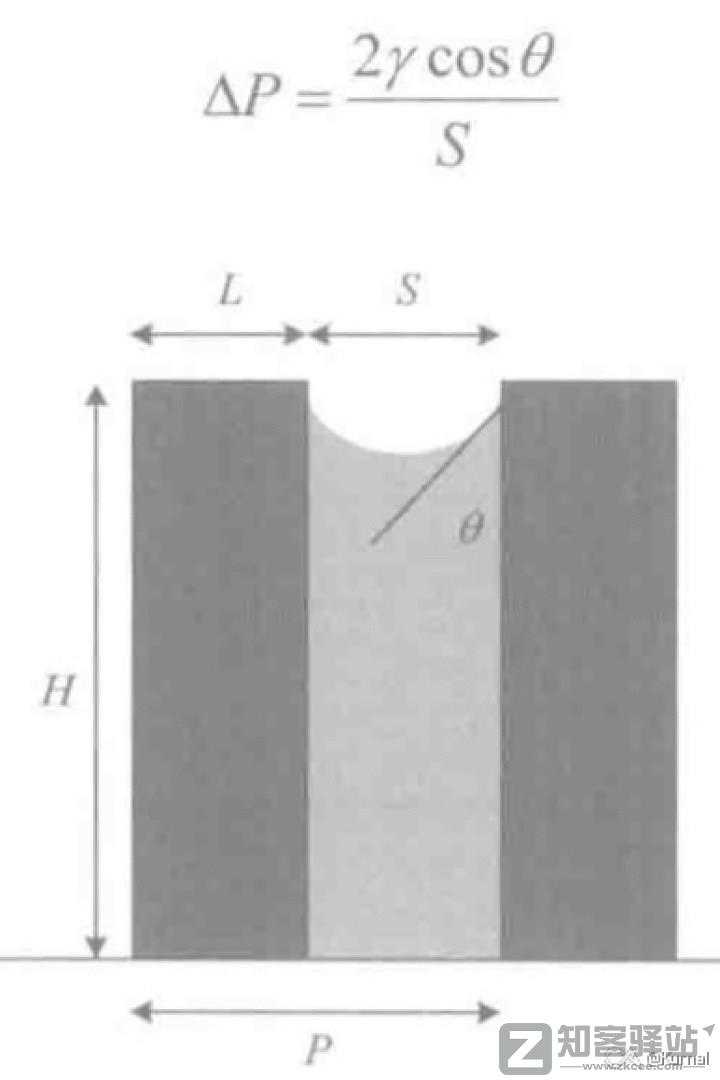

还有就是显影单元,显影单元包括了一个承载晶圆,喷显影液,去离子水以及表面活性物的几个喷嘴。机械手把晶圆放在转台上,喷嘴把显影液喷洒到晶圆表面,然后在规定的显影时间结束后,用去离子水冲洗晶圆,最后转台高速旋转,甩干晶圆讲一个重要的,因为等离子水表面具有一定的表面张力,在干燥的过程中水的张力会施加在光刻胶线条上,会导致光刻胶线条的倒塌。

没了吧,可以讲光刻机了光刻的原理:

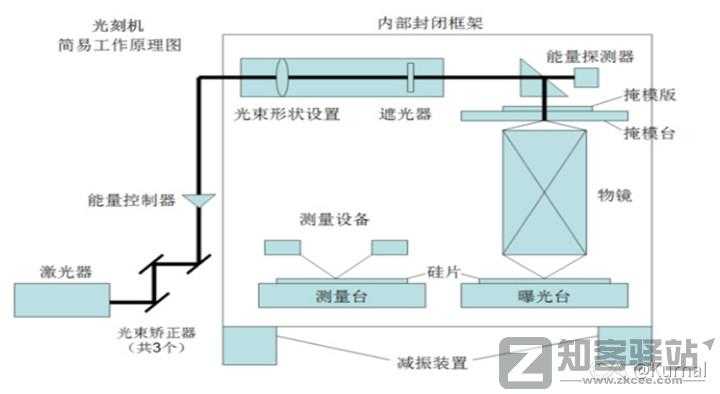

简略图

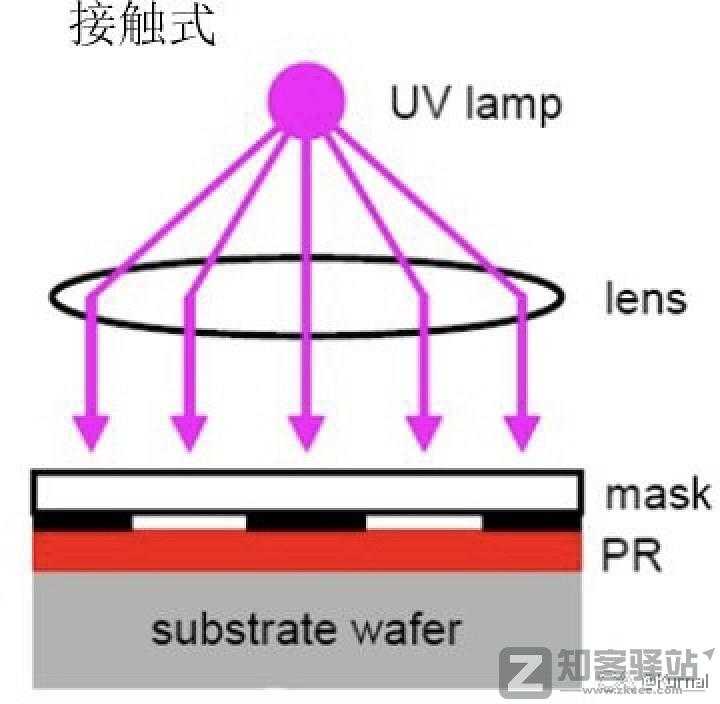

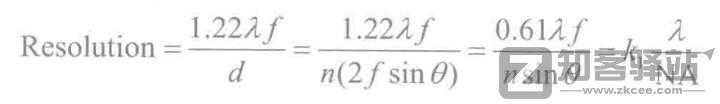

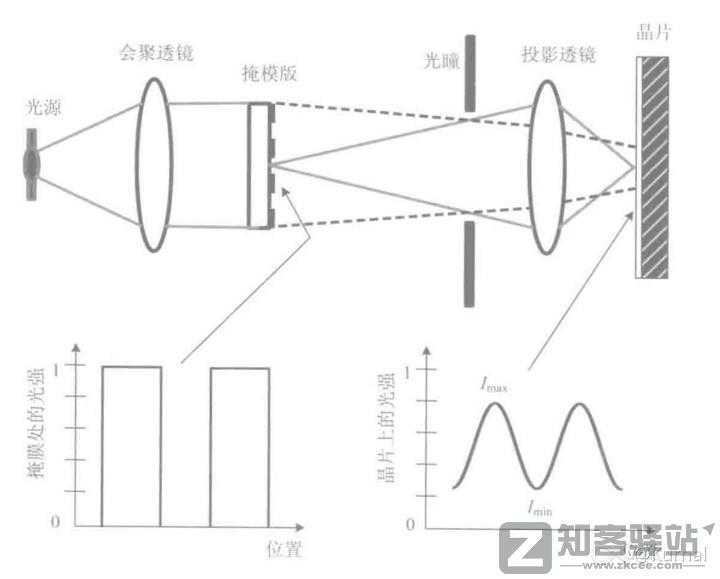

就是曝光,首先是利用光化学反应把实现制备好的mask上的图形转印到sub(一般为Si)的过程,基本分4种,接触式曝光,非接触式曝光,投影式曝光和步进式曝光。接触式曝光是将mask与待加工基板的光胶直接接触进行的曝光,掩膜与基板紧密接触,mask与sub面积一样大,优点是成本低,分辨率高,mask与sub紧密接触,不容易产生衍射现象,缺点就是难分开,mask成本太高,

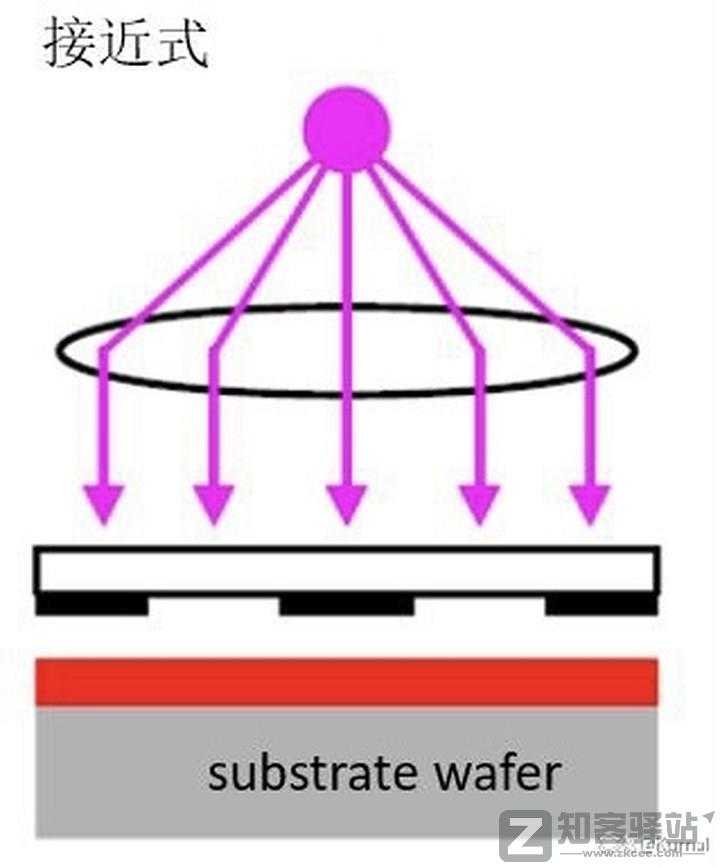

接近式曝光是非接触式曝光的一种,优点就是成本低廉,(因为一片mask可以用好久)缺点就是光的衍射现象

投影式曝光指的是mask与sub不直接接触,采用透镜成像的技术,更一步提高了mask与sub的距离,可以让mask不与sub比例为1;1,做出来的线条可以更细

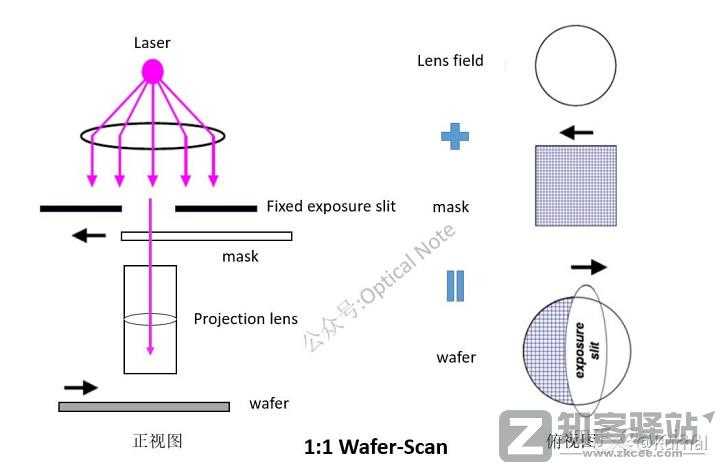

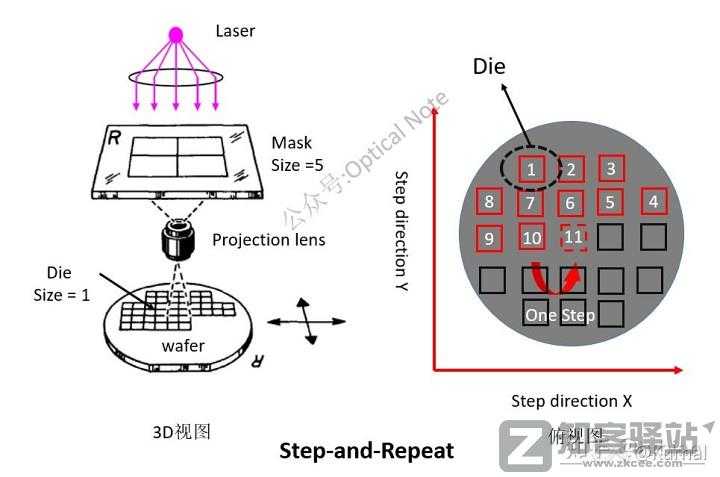

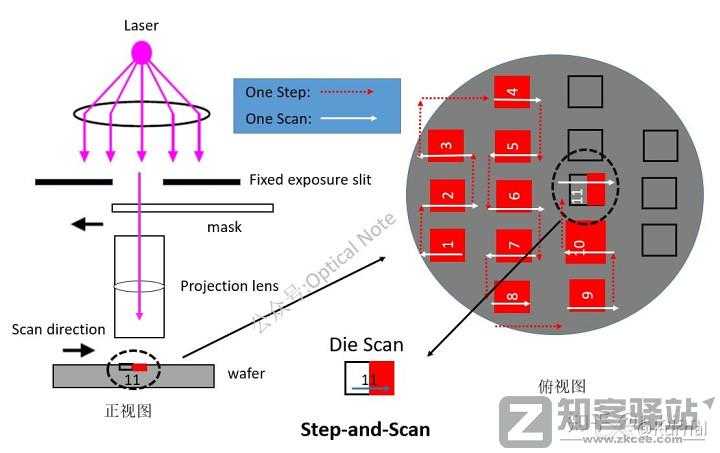

最新的就是步进式曝光,

随着wafer的面积越来越大,如果仍然使用1:1比例的mask,就需要更大的NA,更大的透镜,其可以让在其透镜不变的情况下,把整片wafer分割为一些小die,一般为22mmx22mm,然后通过4;1-5:1的比例做一个die的mask,在第一个die被曝光后用步进器移动wafer让其在切分die里曝光

步进器

一个光刻机里面重要的几个东西,光源,镜头

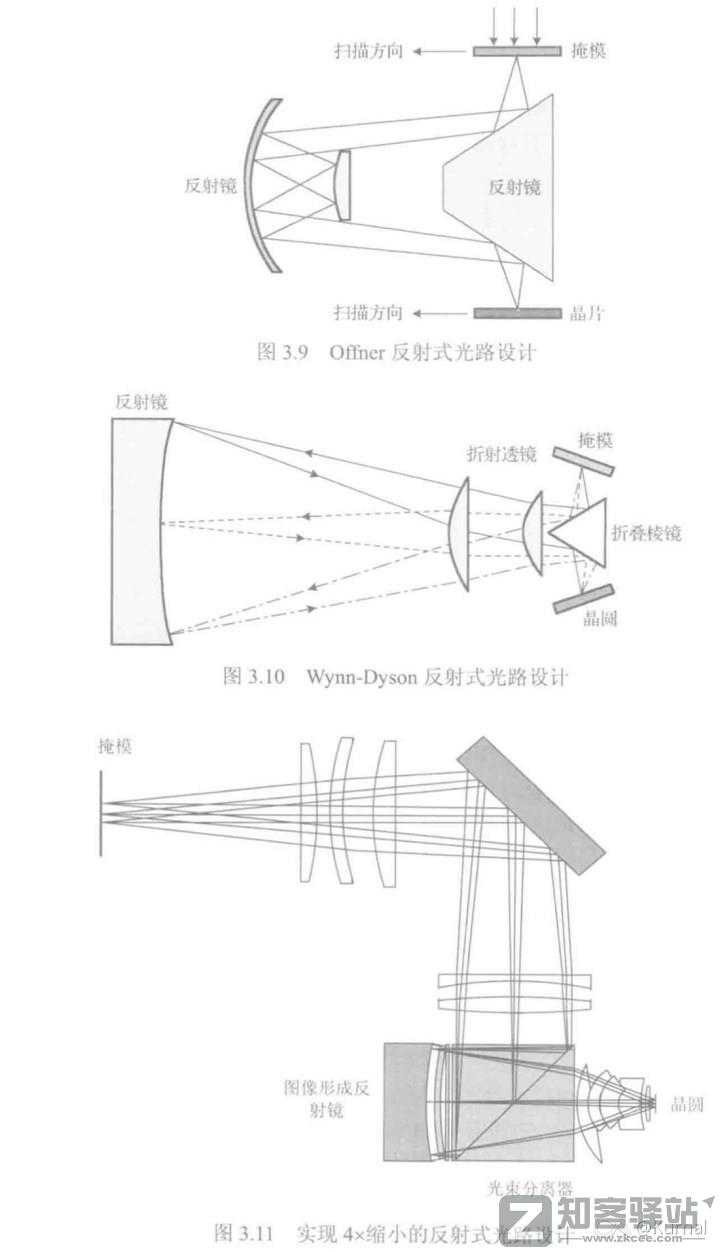

一些光路设计

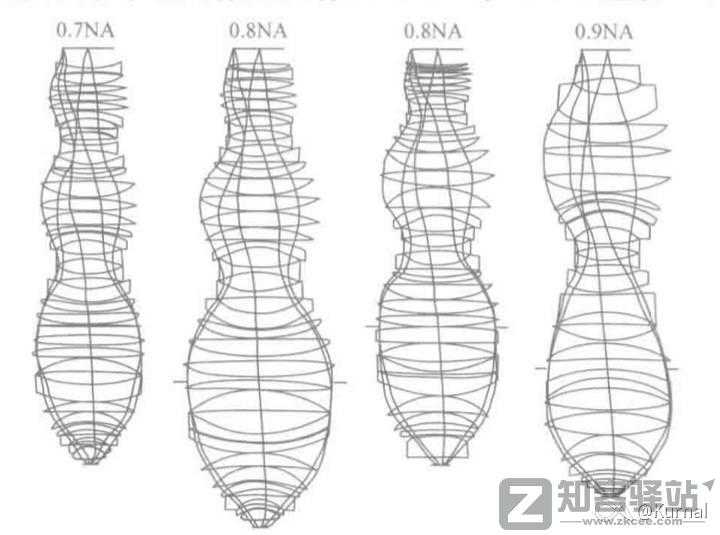

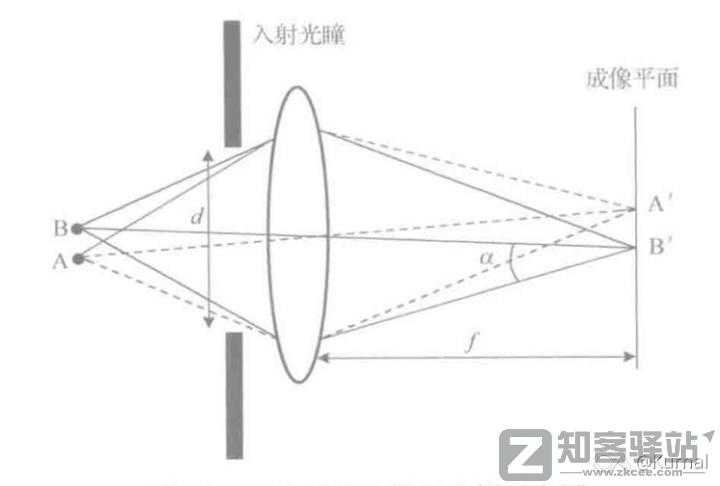

为什么镜头很重要,衡量一个光刻机的指标,最重要的是分辨率(数学小知识课堂)在投影式光刻机的曝光系统可以用koehler光学模型来描述,光源位于会聚透镜的焦平面上,通过会聚透镜后,光线照在mask上,产生衍射光束。投影透镜组的大小决定了有多少的衍射光被收集并聚焦到晶圆表面,较大的镜头将会有更大的分辨率,

mask上相邻的A/B点,在wafer上形成的A1/B1那么A/B间距最小为多少,A1B1才能被清洗掉分辨出来?这就是瑞利公式,即:Resolution=(1.22λf)/d=k1( λ/NA)d是光瞳的孔径,f是透镜的焦距,K1是一个常数,λ是光源的波长,NA是投影透镜的数值孔径定义为nsinθ,对于193nm的浸入式光刻机,n为1.44(因为水在193波中折射),其他取1.0

为了更细,可以改变光源或者数值孔径NA(由公式得)

目前光源一共迭代了4代,早期的G线435nm,再到i射线,波长365nm,然后是深紫外光DUV,Krf为248nm,ArF为193nm,最先进的极紫外光(euv)则为13.5nm,这也是为什么要选择euv的原因

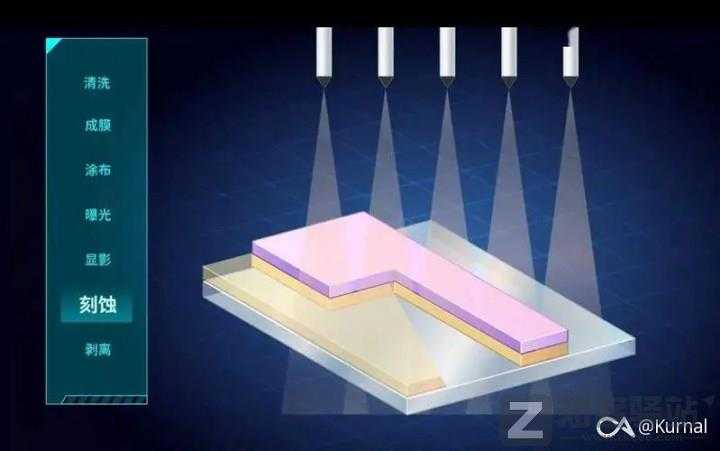

然后就是刻蚀(Etch),与光刻相对应先通过光刻将光刻胶进行光刻曝光处理,然后把硅片上已经显影的光刻胶给进行一个去除或把不显影的光刻胶进行一个去除(凹版凸版罢)

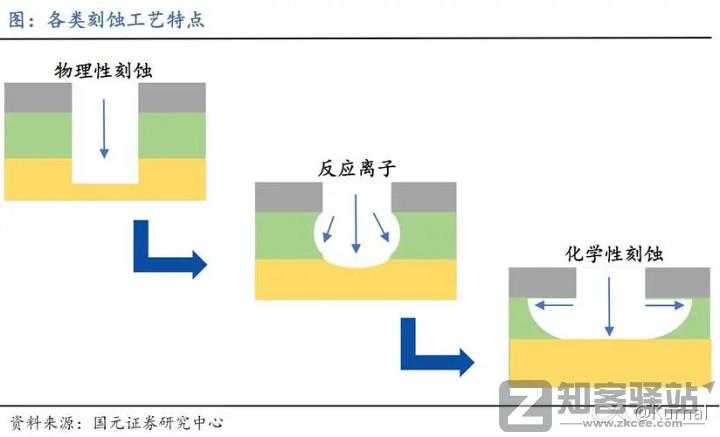

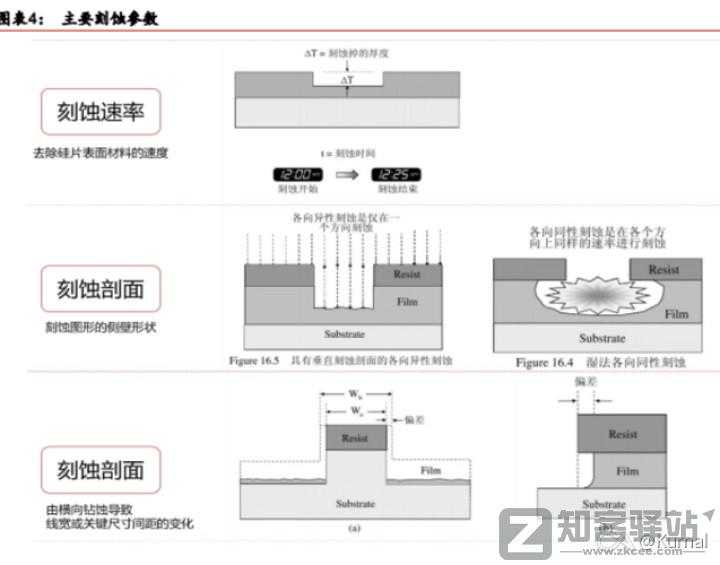

基本分两类,干法刻蚀与湿法刻蚀(说实在的不是这行的人,不是专业的,找了点资料)湿法刻蚀是一种将刻蚀材料浸泡在腐蚀液内进腐蚀的技术,一般为酸/碱合剂一般只是用在尺寸较大的情况下(大于3微米)。在整个fab流程中,湿法腐蚀一般用来腐蚀硅片上某些层或用来去除干法刻蚀后的残留物。通过化学反应腐蚀掉硅片背面及四周的PN结,以达到正面和背面绝缘的目的,缺点是污染环境,其产生废液巨多

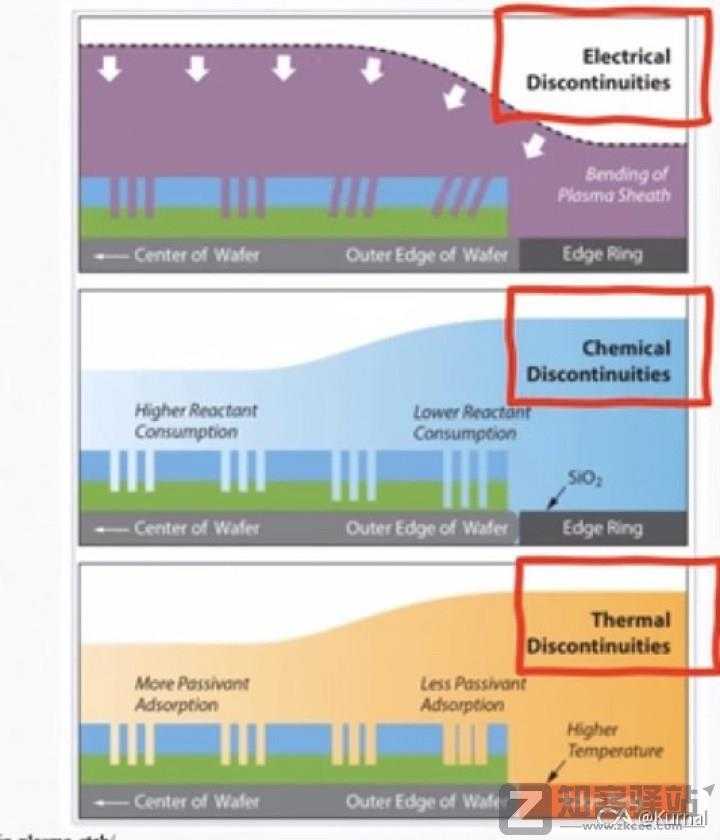

干法刻蚀是把硅片表面曝露于气态中产生的等离子体中,等离子体通过光刻胶中开出的窗口,与硅片发生物理/化学反应,从而去掉曝露的表面材料。

干法可以根据被刻蚀的材料类型来分类,一般分成三种:金属刻蚀、介质刻蚀、和硅刻蚀。介质刻蚀是用于介质材料的刻蚀,如SiO2。硅刻蚀一般用于需要去除硅的场合,如刻蚀多晶硅晶体管栅和硅槽电容。金属刻蚀主要是在金属层上去掉铝合金复合层,制作出互连线。

以BEOL的wafer sub为例,一个三层材料的返工工艺流程(例子):第一次等离子体过程用来去除光刻胶,并使SiARC中的Si成分转化成SiO2,使用的反应气体为O2/N2/H2,其中N2/H2为保护气体,用来控制保护速率,然后用稀释的HF清洗晶圆表面,去掉SiO2,第二次等离子体过程用来去除旋涂的碳(SOC或者叫OPL)使用O2/H2N2,最后再用等离子体冲洗。最后就是离子注入了,原理就是可以看我上一篇图文